Synopsys Standard Cell Libraries

As part of Synopsys Foundation IP portfolio, the high-speed, high-density, and low-power Logic Libraries provide a complete standard cell platform solution for a wide variety of system-on-chip (SoC) designs. In addition to Synopsys' silicon-proven standard cell libraries, available Power Optimization Kits (POKs) and Engineering Change Order (ECO) Kits deliver outstanding performance, with low power and small area in the advanced nodes of leading foundries.

Ideal for tablet, smartphone, cell phone, graphics, networking, storage, and other high-performance applications requiring low power and high density, Synopsys Logic Libraries and Memory Compilers provide a unique set of options that enable SoC designers to optimize their products for speed, area, dynamic power, standby power, and cost.

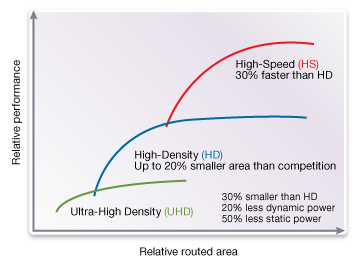

Multiple Architectures, Multiple VTs, Multi-Channel LengthsThe standard cell libraries provide three separate architectures, high-speed (HS), high-density (HD), and ultra high-density (UHD), to optimize circuits for performance, power and area tradeoffs.

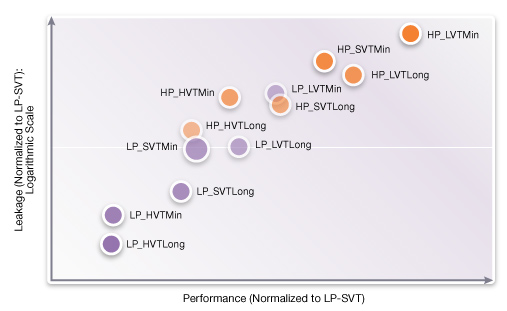

The standard cell libraries include multiple voltage threshold implants (VTs) at most processes from 180-nm to 3-nm and support multiple channel (MC) gate lengths to minimize leakage power at 40-nm and below.

Synopsys Embedded Memories and Logic Libraries are available for multiple foundries and process technologies, including GLOBALFOUNDRIES, SMIC, TSMC, and UMC.

Synopsys Foundation IP Datasheets![]() Synopsys Adaptive Body Bias (ABB) Subsystem for GF 22FDX/22FDX+ Datasheet

Synopsys Adaptive Body Bias (ABB) Subsystem for GF 22FDX/22FDX+ Datasheet![]() Synopsys Foundation IP for GF 22FDX Datasheet

Synopsys Foundation IP for GF 22FDX Datasheet![]() Synopsys Foundation IP for GF 22FDX+ Datasheet

Synopsys Foundation IP for GF 22FDX+ Datasheet![]() Synopsys Foundation IP for GF 40LP Datasheet

Synopsys Foundation IP for GF 40LP Datasheet![]() Synopsys Foundation IP for GF 55LPe Datasheet

Synopsys Foundation IP for GF 55LPe Datasheet![]() Synopsys Foundation IP for SMIC 40LL Datasheet

Synopsys Foundation IP for SMIC 40LL Datasheet![]() Synopsys Foundation IP for SMIC 65LL Datasheet

Synopsys Foundation IP for SMIC 65LL Datasheet![]() Synopsys Foundation IP for TSMC 16FF+ Datasheet

Synopsys Foundation IP for TSMC 16FF+ Datasheet![]() Synopsys Foundation IP for TSMC 16FFC Datasheet

Synopsys Foundation IP for TSMC 16FFC Datasheet![]() Synopsys Foundation IP for TSMC 22ULL Datasheet

Synopsys Foundation IP for TSMC 22ULL Datasheet![]() Synopsys Foundation IP for TSMC 28HP Datasheet

Synopsys Foundation IP for TSMC 28HP Datasheet![]() Synopsys Foundation IP for TSMC 28HPC Datasheet

Synopsys Foundation IP for TSMC 28HPC Datasheet![]() Synopsys Foundation IP for TSMC 28HPC+ Datasheet

Synopsys Foundation IP for TSMC 28HPC+ Datasheet![]() Synopsys Foundation IP for TSMC 28HPM Datasheet

Synopsys Foundation IP for TSMC 28HPM Datasheet![]() Synopsys Foundation IP for TSMC 40LP Datasheet

Synopsys Foundation IP for TSMC 40LP Datasheet![]() Synopsys Foundation IP for TSMC 65LP Datasheet

Synopsys Foundation IP for TSMC 65LP Datasheet![]() Synopsys Foundation IP for TSMC N4P Datasheet

Synopsys Foundation IP for TSMC N4P Datasheet![]() Synopsys Foundation IP for TSMC N5 Datasheet

Synopsys Foundation IP for TSMC N5 Datasheet![]() Synopsys Foundation IP for TSMC N5A Datasheet

Synopsys Foundation IP for TSMC N5A Datasheet![]() Synopsys Foundation IP for TSMC N6 Datasheet

Synopsys Foundation IP for TSMC N6 Datasheet![]() Synopsys Foundation IP for TSMC N7 Datasheet

Synopsys Foundation IP for TSMC N7 Datasheet![]() Synopsys Foundation IP for UMC 28HLP Datasheet

Synopsys Foundation IP for UMC 28HLP Datasheet![]() Synopsys Foundation IP for UMC 28HPC Datasheet

Synopsys Foundation IP for UMC 28HPC Datasheet![]() Synopsys Foundation IP for UMC 40LP Datasheet

Synopsys Foundation IP for UMC 40LP Datasheet![]() Synopsys Foundation IP for UMC 40ULP Datasheet

Synopsys Foundation IP for UMC 40ULP Datasheet

- Maximum Performance

- High-performance libraries for critical paths of GHz processors

- Close timing in fewer iterations without sacrificing area or power

- Minimum Power

- Multi-channel libraries for 4X-5X static power reduction

- Power Optimization Kits with over 200 cells

- Support for low-power UPF and CPF EDA flows

- Maximum Density

- Patented NXT standard cell architectures for highest routing utilization

- Multiple cell heights (# tracks) per process for optimal tradeoffs

- Hand-crafted layout for maximum density

- Deep cell set of functions and drive strengths for optimal cell choice

- Optimal pin placement for highest routed density

- High Yield

- Design-for-manufacturing (DFM)-aware design and validation

- Redundant contacts

- Electro-migration (EM)-compliant at the highest speeds

- Comprehensive Solution

- Electrically, physically and EDA-view aligned with Synopsys Embedded Memory products

- Multi-VDD characterization with low voltage and overdrive PVTs

- Multiple Libraries per Process Node

- Base Libraries include cell set in multiple architectures/ VTs at minimum channel length

- Multiple Channel Length Libraries (MC) for leakage reduction at 40-nm and smaller and to reduce die-to-die leakage and timing variability

- Power Optimization Kits enable shut-down and multiple voltage domains

- ECO Kits enable metal-only post-silicon fixes to cost-effectively address bugs

- High Performance Core (HPC) Design Kits offered at 40-nm and smaller with datapath cells and multi-bit flip-flops

- Metal-programmable libraries for flexible, metal-only design changes over life of product

- Ultra Low Leakage Libraries provide up to 100X leakage reduction for building always-on blocks

- Multiple Cell Architectures for Optimal Power, Performance, and Area

- High-Speed (tall) library for the ultimate in performance for critical paths

- High-Density (short) library for general purpose logic with balanced PPA

- Ultra-High Density (shortest) library for lowest power, lowest cost and highest density

- Optimized Cell Sets

- Rich synthesis-friendly cell set with multiple cell variants and drive strengths

- Specialty cells such as integrated clock gaters (ICG), multi-bit flip-flops and routing support cells

- Accurate Characterization

- HSPICE® accuracy

- Propagation delays and constraints (Setup, Hold, Removal & Recovery, Minimum Pulse Width)

- Corner specific extraction at advanced nodes

- EDA Views

- Liberty® Timing, Noise and Power, CCS Timing, Noise and ECSM Timing

- Other specialty models

- Availability of Process, Voltage, and Temperature (PVT) Characterization Corners

- Standard, overdrive and low voltage PVT clusters for timing and leakage

- PVTs aligned with Synopsys Memory Compiler PVTs

- Custom PVT development available

- Silicon proven using Split Lots at Advanced Nodes

- Correlated to EDA models

- Low voltage testing to VDDMin